欢迎来到m6体育(中国)科技有限公司官方网站!

光耦合器_CMOS 数字隔离器的安全认证及特性介绍

2021-11-25 来源:

m6体育(中国)科技有限公司

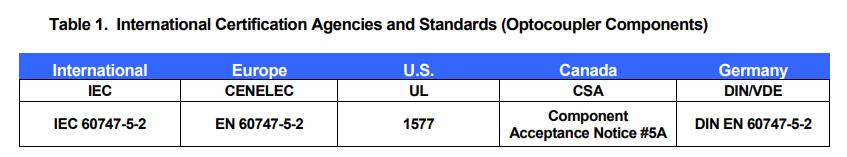

国际安全标准提供了测试方法和指南,以确保终端设备免受电击、机械危险、火灾和电磁干扰的影响。下表里按地理位置总结了光耦合器和其他隔离器(包括CMOS数字隔离器)的组件级国际安全标准。

认证测试包括使隔离器组件承受测试标准规定的各种应力,同时监测被测设备是否存在可能危及安全的故障。

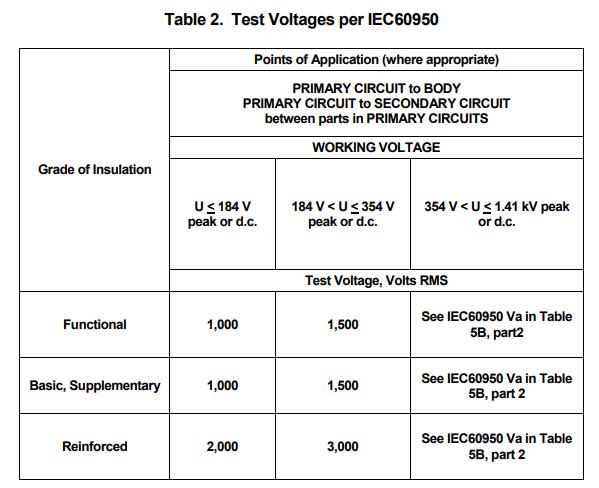

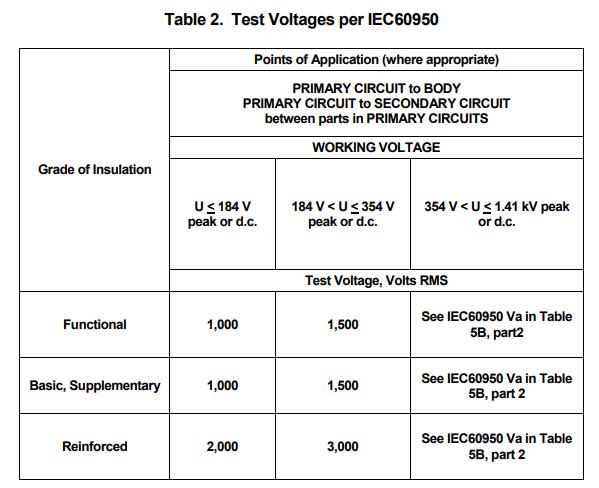

上表Table 2里,摘自IEC60950规定的电气强度试验。所示测试电压假设均匀连接的封装表面,如仅模塑化合物。然而,在光耦合器和CMOS数字隔离器的隔离栅中使用了不同的材料。

上表Table 2里,摘自IEC60950规定的电气强度试验。所示测试电压假设均匀连接的封装表面,如仅模塑化合物。然而,在光耦合器和CMOS数字隔离器的隔离栅中使用了不同的材料。

例如,CMOS数字隔离器使用二氧化硅作为初级绝缘体,塑料模化合物作为次级绝缘体。这种类型的非均质连接结构称为“水泥接头”,要求认证机构通过将表2的试验电压增加1.6倍来验证隔离器。例如,支持峰值或直流工作电压为354 V的加固部件必须耐受4800 VACRMS介电耐受电位1分钟,才能通过机构认证的额定电压为4800 VACRMS。此外,制造商对该隔离器的生产测试必须包括在120%额定值下测试每个部件1秒。因此,上述354 V隔离器将在5760 VACRMS(4800 Vrms x 1.2)下进行1秒的生产测试,以确保其完整性。

操作功率

至少,光耦合器需要电流来偏置LED,并在输出侧施加某种形式的偏置。根据光耦的类型,总输入加输出电流变化很大。当正向偏置时,光耦LED为低阻抗,器件功耗随着LED正向电流的增加而增加,其范围从1 mA到15 mA以上。在某些情况下,LED可能需要外部驱动器,从而进一步降低系统m6体育,同时增加BOM复杂性和成本。根据其结构,光耦输出阻抗可以低也可以高。大多数低成本的光耦都有一个简单的晶体管输出,当LED正向电流为零时,该输出具有高阻抗,而当LED正向电流处于其指定的工作范围时,该输出具有相对较低的阻抗。其他(通常速度更高)光耦具有有源光耦合器和需要外部偏置电压的输出驱动器。此类设备的输出阻抗较低,但总工作电流增加,其范围从15 mA到40 mA以上。

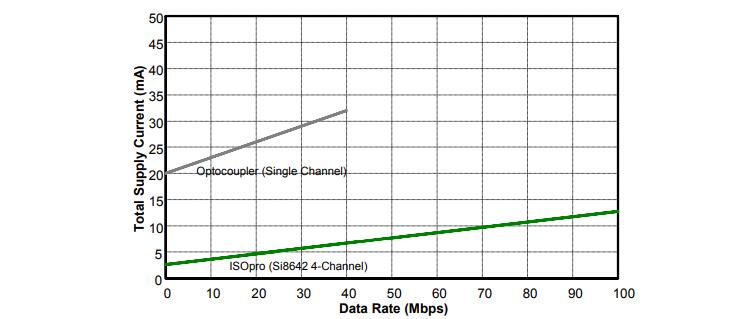

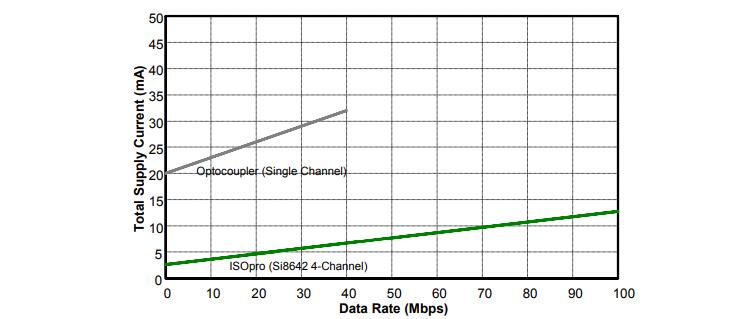

与光耦相比,CMOS数字隔离器提供了更高的工作m6体育,在VDD=5.0 V和15 pF负载下,以10 Mbps的速度每通道消耗约1.7 mA。其高阻抗输入缓冲器仅消耗微安的泄漏电流,而其50 CMOS输出驱动器可以源或汇4 mA。CMOS数字隔离器的大部分功率节省源于使用射频载波而不是光,从而消除了耗电的LED。通过隔离电容器结构将隔离路径中的损耗降至最低,该结构针对稳健的数据传输和最小的功率损耗进行了优化。CMOS数字隔离器的功耗保持相对平坦,基本上低于光耦。供电电流增加的唯一值得注意的因素是数据速率的增加,然而,如图6所示,即使这种增加也相对较浅。

鉴于工业设备的典型使用寿命,长期可靠性和一致性性能是系统设计师最关心的问题。光耦定时参数(例如传播延迟和脉冲宽度失真)可随三个变量变化:LED磨损、LED电流和工作温度。

鉴于工业设备的典型使用寿命,长期可靠性和一致性性能是系统设计师最关心的问题。光耦定时参数(例如传播延迟和脉冲宽度失真)可随三个变量变化:LED磨损、LED电流和工作温度。

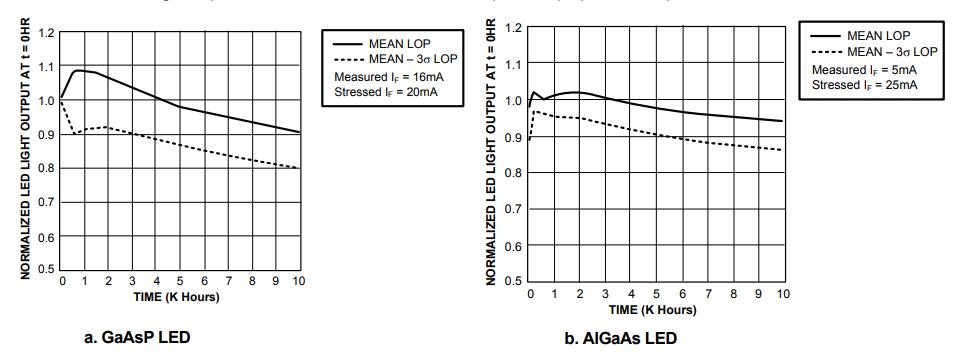

其中一个关键的光耦磨损机制是LED光输出(LOP),这是一种基于材料的现象,会导致LED随着时间的推移失去亮度。较低的发射会降低光电探测器看到的信号,对光耦定时和输出阻抗特性产生负面影响。图7a和7b显示了制造商基于由磷化砷化镓(GaAsP)和砷化铝(AlGaAs)制成的LED在10000小时内的归一化光输出的LOP数据。随着温度的升高和LED电流的增加,光输出退化通常会恶化。在最坏的情况下,光输出可能低于设备正常运行所需的最小值。

定时特性

定时规范在数字隔离器应用中非常重要,以确保系统正常、一致地运行。图8比较了10 Mbps CMOS数字隔离器与竞争性数字光耦的传播延迟特性。使用不同的LED电流测量传播延迟,包括有无“峰值”电容器。

注:在这种情况下,峰值电容器与LED限流电阻器并联20 pF。该电容器在开启和关闭期间瞬时增加LED电流,以实现更快的光耦响应。

共模瞬态抗扰度(CMTI)

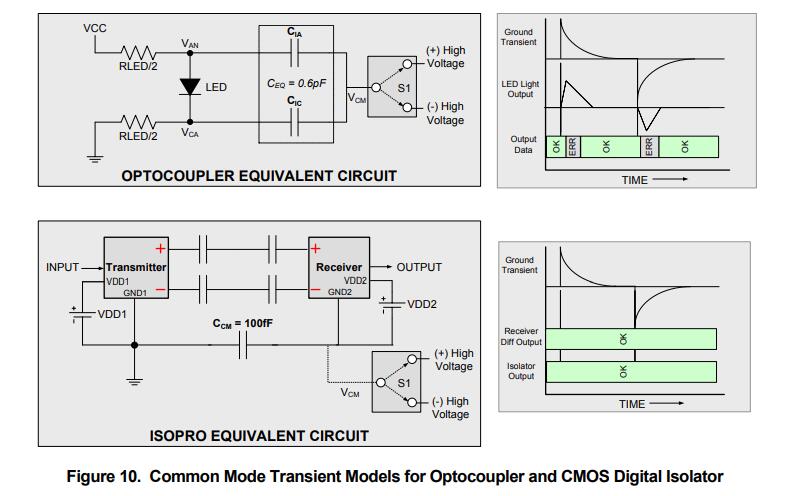

共模瞬态是隔离应用中数据损坏的主要原因之一。CMTI通常以千伏/微秒为单位测量,指隔离器抑制隔离器输入和输出之间噪声的能力。图9a显示了受到共模噪声VCM影响的光耦。当VCM因快速瞬变而改变时,iLP和iLN会帮助或反对LED电流,导致LED发光的瞬间变化,通常尽管制造商添加了探测器屏蔽以减少寄生电容输入/输出耦合。

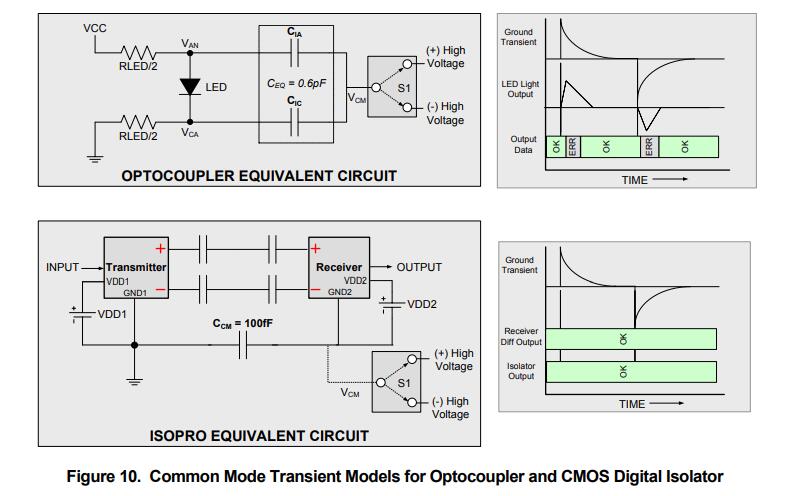

(图片名称)Optocoupler Equivalent Circuit

接地之间的光耦寄生耦合通常在十分之一微微法拉的范围内(例如,Avago HCPL-0703为0.6 pF),这大大降低了CMTI。使用图10所示的“准差分”驱动可以获得一定程度的CMTI改善,其中LED限流电阻器放置在LED的两侧,每个电阻的值为图9中RLED的一半。

如图10的光耦时序图所示,光耦右侧接地(相对于左侧接地)上的正向接地瞬态会导致LED电流瞬时增加。根据瞬态的大小和光耦中存在的寄生耦合量,该LED“故障”可能导致数据错误。例如,0.6 pF耦合可能足以在LED应保持关闭时错误地瞬时打开LED。同样,负向瞬态可能会在LED保持点亮时错误地关闭LED。光耦制造商发布的应用手册中详细讨论了光耦固有的低CMTI,其中一些建议在高共模环境下工作时,在开启状态下过度驱动LED,在关闭状态下反向偏置LED。虽然这种技术是有效的,但它增加了LED的功耗,并加速了LOP造成的损耗。在任何情况下,寄生耦合都是不可避免的,并且会降低光耦CMTI的性能。

如图10的光耦时序图所示,光耦右侧接地(相对于左侧接地)上的正向接地瞬态会导致LED电流瞬时增加。根据瞬态的大小和光耦中存在的寄生耦合量,该LED“故障”可能导致数据错误。例如,0.6 pF耦合可能足以在LED应保持关闭时错误地瞬时打开LED。同样,负向瞬态可能会在LED保持点亮时错误地关闭LED。光耦制造商发布的应用手册中详细讨论了光耦固有的低CMTI,其中一些建议在高共模环境下工作时,在开启状态下过度驱动LED,在关闭状态下反向偏置LED。虽然这种技术是有效的,但它增加了LED的功耗,并加速了LOP造成的损耗。在任何情况下,寄生耦合都是不可避免的,并且会降低光耦CMTI的性能。

图10的底图显示了CMOS数字隔离器及其共模电压VCM和100毫法拉输入输出电容(CCM),其比光耦小六倍。其全差分隔离路径可抑制共模电压,接收器的高选择性可抑制除载波频率以外的所有频率,从而获得更大的抗噪性。由于这些原因,CMOS数字隔离器的典型CMTI为60 kV/µs,大大高于大多数使用外部组件改善CMTI的光耦。

电磁干扰(EMI)

EMI指干扰或以其他方式干扰授权电气设备有效性能的任何电磁干扰。由于涉及隔离器,辐射和传导EMI通常是高频开关电路(及其谐波)的产物,这些电路耦合到其他电路和/或环境中。辐射EMI类似于广播,因为它通过自由空间从发射机传播到接收机,而传导EMI沿着导体传播。FCC规定了传导和辐射EMI的限制,且给定类别的所有设备必须符合这些标准。

各机构发布的规范对传导和辐射EMI进行了限制。FCC第15部分是较为常见的规范之一,该部分涵盖了家庭或家庭附近使用的电路组件。本规范的测试在露天环境中进行,使用距离地面约5米的10米天线。

另一个规范SAEJ1752-3的测试方法更以IC为中心,建议将待测试的IC安装在小型电路板上,并在实际应用环境中运行时测量电路板的辐射发射。对于本试验,CISPR-25(汽车EMI规范SAE J1113的子集)规定了各种频带的辐射EMI限值。

使用两块测试板进行FCC B类第15部分的EMI测试,每块测试板包含一个嵌套6通道CMOS数字隔离器,所有输入连接高,以最大限度地增加内部发射机的发射(即,在两块嵌套板上以全速切换12通道)。CMOS数字隔离器通过FCC B类第15部分,尽管使用了增加EMI发射的插座。CMOS数字隔离器主要通过组合场抵消内部差分信号路径、隔离电容的大小以及低功率主振荡器的设计来实现低EMI操作。根据要求,可从硅实验室获得EMI图。

射频抗扰度

射频抗扰度是隔离器拒绝强局部电磁场的能力,从而保持无误数据传输。直观地说,可以假设环境射频场会干扰CMOS数字隔离器的内部射频数据传输。然而,CMOS数字隔离器凭借其设计表现出极高的外部射频噪声抑制程度。

局部场在CMOS数字隔离器的内部信号路径内感应共模电压,该共模电压被CMOS数字隔离器的差分隔离信号路径和高接收器选择性的组合所拒绝。CMOS数字隔离器内部差分信号路径两侧的信号电平紧密匹配,导致接收器输入端的共模电压被拒绝。然后,接收器仅在非常窄的频带内放大差分输入电压,并拒绝所有其他输入。总之,这些机制拒绝来自外部磁场的干扰,并在工业应用中常见的恶劣电气环境中实现非常高的CMTI和稳健的操作。

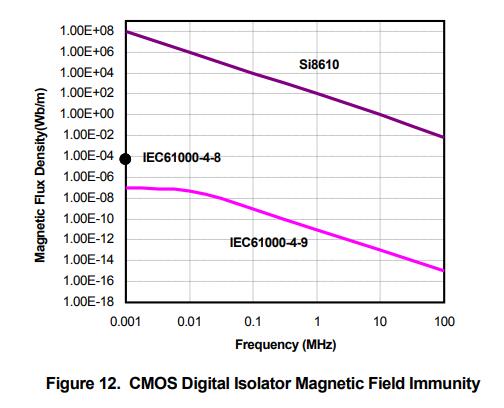

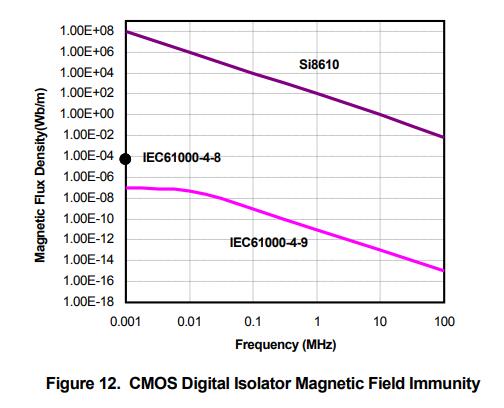

如图12所示,CMOS数字隔离器的磁场抗扰度使其能够在大型电机和其他磁场产生设备附近使用。如果磁场太m6体育/或离隔离器太近,理论上可能会发生数据传输错误。然而,在实际使用中,CMOS数字隔离器对外部磁场具有极高的抗扰度,并且经过独立评估,能够承受至少1000 A/米的磁场(根据IEC 61000-4-8和IEC 61000-4-9规范)。通过距离CMOS数字隔离器0.1 m的0.1 m导体,可产生107安培的此类磁场。在任何操作环境中都不太可能发现这种情况。在损坏CMOS隔离器的隔离栅之前,这样的磁场很可能会破坏周围的电路。此外,CMOS数字隔离器具有独立实验室测量的高电场抗扰度(最小20 V/米)。

如图12所示,CMOS数字隔离器的磁场抗扰度使其能够在大型电机和其他磁场产生设备附近使用。如果磁场太m6体育/或离隔离器太近,理论上可能会发生数据传输错误。然而,在实际使用中,CMOS数字隔离器对外部磁场具有极高的抗扰度,并且经过独立评估,能够承受至少1000 A/米的磁场(根据IEC 61000-4-8和IEC 61000-4-9规范)。通过距离CMOS数字隔离器0.1 m的0.1 m导体,可产生107安培的此类磁场。在任何操作环境中都不太可能发现这种情况。在损坏CMOS隔离器的隔离栅之前,这样的磁场很可能会破坏周围的电路。此外,CMOS数字隔离器具有独立实验室测量的高电场抗扰度(最小20 V/米)。

静电放电(ESD)和电过应力(EOS)

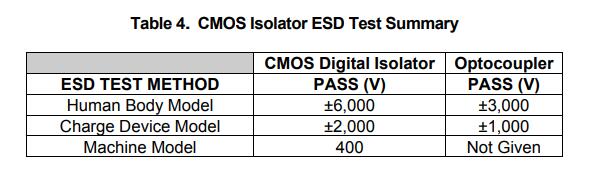

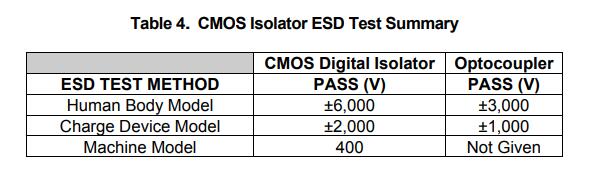

ESD和EOS事件(如快速瞬变和浪涌)可由多种原因引起,包括交流线路偏移、接地之间的共模瞬变、雷击和人为操作。ESD是这些应力的一个子集,IC封装级别的测试提供了与组件处理相关的设备稳健性测量(见表4)。

虽然CMOS数字隔离器比大多数光耦具有更高的ESD抗扰度,但需要注意的是,测试包括将ESD直接应用于无电源隔离器引脚。然而,一旦安装在电路板上,隔离器就会成为较大电路的一部分,在较大电路中,处理相关ESD冲击通常会扩散到低阻抗电路路径上。因此,具有6 kV ESD额定值的隔离器可在具有15 kV ESD事件的系统内可靠运行。必须在系统级别解决针对其他EOS应力的保护问题。这些考虑因素包括用于最小化噪声的适当布局技术、仔细注意短跟踪路径以最小化串联电感(从而减小电路振铃)、适当的偏置电源接地、布线和滤波,以及防止电压和电流浪涌。

虽然CMOS数字隔离器比大多数光耦具有更高的ESD抗扰度,但需要注意的是,测试包括将ESD直接应用于无电源隔离器引脚。然而,一旦安装在电路板上,隔离器就会成为较大电路的一部分,在较大电路中,处理相关ESD冲击通常会扩散到低阻抗电路路径上。因此,具有6 kV ESD额定值的隔离器可在具有15 kV ESD事件的系统内可靠运行。必须在系统级别解决针对其他EOS应力的保护问题。这些考虑因素包括用于最小化噪声的适当布局技术、仔细注意短跟踪路径以最小化串联电感(从而减小电路振铃)、适当的偏置电源接地、布线和滤波,以及防止电压和电流浪涌。

认证测试包括使隔离器组件承受测试标准规定的各种应力,同时监测被测设备是否存在可能危及安全的故障。

例如,CMOS数字隔离器使用二氧化硅作为初级绝缘体,塑料模化合物作为次级绝缘体。这种类型的非均质连接结构称为“水泥接头”,要求认证机构通过将表2的试验电压增加1.6倍来验证隔离器。例如,支持峰值或直流工作电压为354 V的加固部件必须耐受4800 VACRMS介电耐受电位1分钟,才能通过机构认证的额定电压为4800 VACRMS。此外,制造商对该隔离器的生产测试必须包括在120%额定值下测试每个部件1秒。因此,上述354 V隔离器将在5760 VACRMS(4800 Vrms x 1.2)下进行1秒的生产测试,以确保其完整性。

操作功率

至少,光耦合器需要电流来偏置LED,并在输出侧施加某种形式的偏置。根据光耦的类型,总输入加输出电流变化很大。当正向偏置时,光耦LED为低阻抗,器件功耗随着LED正向电流的增加而增加,其范围从1 mA到15 mA以上。在某些情况下,LED可能需要外部驱动器,从而进一步降低系统m6体育,同时增加BOM复杂性和成本。根据其结构,光耦输出阻抗可以低也可以高。大多数低成本的光耦都有一个简单的晶体管输出,当LED正向电流为零时,该输出具有高阻抗,而当LED正向电流处于其指定的工作范围时,该输出具有相对较低的阻抗。其他(通常速度更高)光耦具有有源光耦合器和需要外部偏置电压的输出驱动器。此类设备的输出阻抗较低,但总工作电流增加,其范围从15 mA到40 mA以上。

与光耦相比,CMOS数字隔离器提供了更高的工作m6体育,在VDD=5.0 V和15 pF负载下,以10 Mbps的速度每通道消耗约1.7 mA。其高阻抗输入缓冲器仅消耗微安的泄漏电流,而其50 CMOS输出驱动器可以源或汇4 mA。CMOS数字隔离器的大部分功率节省源于使用射频载波而不是光,从而消除了耗电的LED。通过隔离电容器结构将隔离路径中的损耗降至最低,该结构针对稳健的数据传输和最小的功率损耗进行了优化。CMOS数字隔离器的功耗保持相对平坦,基本上低于光耦。供电电流增加的唯一值得注意的因素是数据速率的增加,然而,如图6所示,即使这种增加也相对较浅。

其中一个关键的光耦磨损机制是LED光输出(LOP),这是一种基于材料的现象,会导致LED随着时间的推移失去亮度。较低的发射会降低光电探测器看到的信号,对光耦定时和输出阻抗特性产生负面影响。图7a和7b显示了制造商基于由磷化砷化镓(GaAsP)和砷化铝(AlGaAs)制成的LED在10000小时内的归一化光输出的LOP数据。随着温度的升高和LED电流的增加,光输出退化通常会恶化。在最坏的情况下,光输出可能低于设备正常运行所需的最小值。

图:光耦制造商的LOP测试数据

如图所示,LOP可将标称光输出改变高达20%(图a),从而导致工作特性的显著变化。此外,由于LOP退化率部分与LED电流有关,因此系统设计师在选择LED正向电流工作范围时必须考虑LOP的影响。例如,较低的LED驱动电流可以换取较长的设备使用寿命,但共模瞬态抗扰度(CMTI)较低。相反,更高的LED驱动电流可用于改善CMTI,但缩短光耦使用寿命。Silicon Labs的CMOS数字隔离器在额定工作条件下使用时不会受到任何磨损机制的影响。定时特性

定时规范在数字隔离器应用中非常重要,以确保系统正常、一致地运行。图8比较了10 Mbps CMOS数字隔离器与竞争性数字光耦的传播延迟特性。使用不同的LED电流测量传播延迟,包括有无“峰值”电容器。

注:在这种情况下,峰值电容器与LED限流电阻器并联20 pF。该电容器在开启和关闭期间瞬时增加LED电流,以实现更快的光耦响应。

共模瞬态抗扰度(CMTI)

共模瞬态是隔离应用中数据损坏的主要原因之一。CMTI通常以千伏/微秒为单位测量,指隔离器抑制隔离器输入和输出之间噪声的能力。图9a显示了受到共模噪声VCM影响的光耦。当VCM因快速瞬变而改变时,iLP和iLN会帮助或反对LED电流,导致LED发光的瞬间变化,通常尽管制造商添加了探测器屏蔽以减少寄生电容输入/输出耦合。

(图片名称)Optocoupler Equivalent Circuit

接地之间的光耦寄生耦合通常在十分之一微微法拉的范围内(例如,Avago HCPL-0703为0.6 pF),这大大降低了CMTI。使用图10所示的“准差分”驱动可以获得一定程度的CMTI改善,其中LED限流电阻器放置在LED的两侧,每个电阻的值为图9中RLED的一半。

图10的底图显示了CMOS数字隔离器及其共模电压VCM和100毫法拉输入输出电容(CCM),其比光耦小六倍。其全差分隔离路径可抑制共模电压,接收器的高选择性可抑制除载波频率以外的所有频率,从而获得更大的抗噪性。由于这些原因,CMOS数字隔离器的典型CMTI为60 kV/µs,大大高于大多数使用外部组件改善CMTI的光耦。

电磁干扰(EMI)

EMI指干扰或以其他方式干扰授权电气设备有效性能的任何电磁干扰。由于涉及隔离器,辐射和传导EMI通常是高频开关电路(及其谐波)的产物,这些电路耦合到其他电路和/或环境中。辐射EMI类似于广播,因为它通过自由空间从发射机传播到接收机,而传导EMI沿着导体传播。FCC规定了传导和辐射EMI的限制,且给定类别的所有设备必须符合这些标准。

各机构发布的规范对传导和辐射EMI进行了限制。FCC第15部分是较为常见的规范之一,该部分涵盖了家庭或家庭附近使用的电路组件。本规范的测试在露天环境中进行,使用距离地面约5米的10米天线。

另一个规范SAEJ1752-3的测试方法更以IC为中心,建议将待测试的IC安装在小型电路板上,并在实际应用环境中运行时测量电路板的辐射发射。对于本试验,CISPR-25(汽车EMI规范SAE J1113的子集)规定了各种频带的辐射EMI限值。

使用两块测试板进行FCC B类第15部分的EMI测试,每块测试板包含一个嵌套6通道CMOS数字隔离器,所有输入连接高,以最大限度地增加内部发射机的发射(即,在两块嵌套板上以全速切换12通道)。CMOS数字隔离器通过FCC B类第15部分,尽管使用了增加EMI发射的插座。CMOS数字隔离器主要通过组合场抵消内部差分信号路径、隔离电容的大小以及低功率主振荡器的设计来实现低EMI操作。根据要求,可从硅实验室获得EMI图。

射频抗扰度

射频抗扰度是隔离器拒绝强局部电磁场的能力,从而保持无误数据传输。直观地说,可以假设环境射频场会干扰CMOS数字隔离器的内部射频数据传输。然而,CMOS数字隔离器凭借其设计表现出极高的外部射频噪声抑制程度。

局部场在CMOS数字隔离器的内部信号路径内感应共模电压,该共模电压被CMOS数字隔离器的差分隔离信号路径和高接收器选择性的组合所拒绝。CMOS数字隔离器内部差分信号路径两侧的信号电平紧密匹配,导致接收器输入端的共模电压被拒绝。然后,接收器仅在非常窄的频带内放大差分输入电压,并拒绝所有其他输入。总之,这些机制拒绝来自外部磁场的干扰,并在工业应用中常见的恶劣电气环境中实现非常高的CMTI和稳健的操作。

静电放电(ESD)和电过应力(EOS)

ESD和EOS事件(如快速瞬变和浪涌)可由多种原因引起,包括交流线路偏移、接地之间的共模瞬变、雷击和人为操作。ESD是这些应力的一个子集,IC封装级别的测试提供了与组件处理相关的设备稳健性测量(见表4)。